## **Application Configurable System Cells**

### Description

Application Configurable System Cells (ACSCs), have been developed by Dialog Semiconductor for specific market segments. The System Cells consist of primary groups of function blocks which have been targeted at individual applications. The Design Engineer is able to utilize these blocks to build his system, and if necessary, have them customized by Dialog to exactly meet his requirements. Proven ASIC design and process technology mean that the circuits provide costeffective and extremely reliable solutions to of within variety manufacturers а fields. Manufacturers benefit from a highly developed application-oriented product, with the added advantage that while it can be fully customized, both development times and risk factors can be significantly reduced. The concept allows the Design Engineer to build a system from proven high level circuit blocks, rather than designing at the standard cell or transistor level.

In any given market place the main participants are usually offering similar products. They differentiate themselves by offering variations on price, performance or functionality. One of the ways they can achieve differentiation is by developing ASICs which encapsulate these benefits. However, many of these potential users of ASICs may be concerned by what they perceive as risk or expense or long development time.

What is required by many system companies is a kind of 'instant ASIC' - the end result without the pain. With this in mind, Dialog has developed its ACSC strategy. ACSC is an attempt to distil the key

### In summary ACSCs are:

- A group of 'Expert Cells' targeted to a specific application

- A fully characterized mixed signal sub-system

- Usually available as packaged parts

attributes of a given application into high level cells to which systems developers have access. By analyzing the common features of a market or application and then pre-developing the main blocks, most of the risk and much of the time element is removed from the equation. Individual systems developers can add as much or as little to the ACSC blocks as they wish. Indeed, the ACSC blocks can be used in standalone mode as discrete ICs, if preferred and, in fact, this may be the best way to start.

A system developer can design-in an ACSC like an ASSP and even go into production with it. As more is learned about the system, or if market feedback suggests it, changes may be required. With any sort of ASSP or standard product, changes are a major problem and can be lengthy and expensive. The ACSC, however, is designed to be flexible and modifying its performance or behaviour is intended to be straightforward. At heart, the ACSC is a technology demonstrator and adding circuitry around it is welcomed as a way of introducing more companies to the benefits of mixed signal ASICs

ACSCs developed by Dialog Semiconductor are targeted to vertical markets, for example, Satellite Communications, Video, Automotive, Security, and Utilities Metering applications.

Dialog has had extensive ASIC experience in the automotive field. Using this experience, Dialog has created a range of Major and Minor ACSC blocks to support our customers in specifying and designing ASICs for their automotive products.

### Main benefits for the system user:

- Allows complete system development when used with field programmable parts

- Short development time

- Can be used to assess market

- Can be used for initial production

- Reduced technical risk

TEMIC

**Dialog Semiconductor**

# ASIC Cells - ACSC

### **Ultrasonic Intrusion Detection Circuit**

### Description

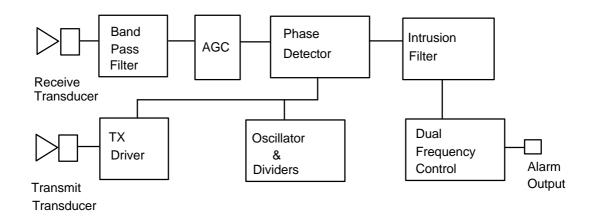

This major ACSC function can either be used as a stand alone circuit, or as part of a larger custom circuit designed to suit specific application requirements. The DA5209 contains all the circuit functions necessary to implement an advanced low power, high sensitivity, ultrasonic movement detection system for automotive applications.

The large AGC range (80dB) of the DA5209 allows it to compensate automatically for the effects of temperature changes, vehicle volume and acoustic absorbency thus removing the need for adjustment at installation. The synchronous demodulator system which monitors both the magnitude and phase of the return signal gives a significant improvement in sensitivity and noise rejection compared to more basic systems. The DA5209 operates at two slightly different signal frequencies under control of a timed sequencer which ensures that an intrusion has occurred at both frequencies before signalling an alarm. The technique avoids false alarms caused by signal cancellation occurring at one of the operating frequencies. The logic level alarm output and power down capability of the DA5209 enable it to be controlled by a microprocessor as part of comprehensive security systems. The DA5209 uses an advanced CMOS technology to enable this level of system integration to be achieved.

#### Features

- Complete stand alone system

- 80dB automatic gain control range

- Sensitive to both amplitude and phase disturbances

- Dual frequency operating mode

- 10mW active power dissipation

- Compact 20 pin SOIC package

TEMIC

**Dialog Semiconductor**

ASIC Cells - ACSC

## High Precision Bridge Sensor Conditioning System

### Description

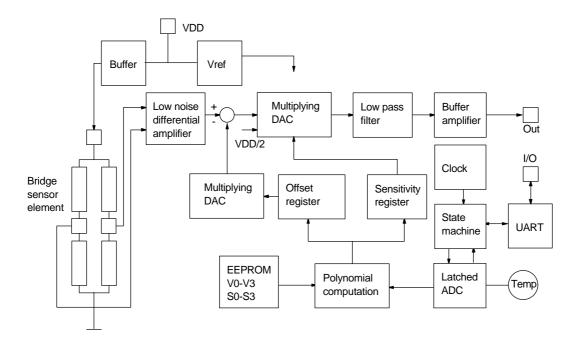

This major ACSC is designed to directly connect to a monolithic bridge sensor and provide a temperature and sensor compensated analog output signal. Digital computation techniques enable a very high calibration resolution. The compensation data is stored in EEPROM which by means of a UART port can easily be calibrated after final assembly of the complete module.

The advantage of this concept is that a sensor with wide manufacturing tolerances can be used and electronically

Features

- Works with low-cost sensors

- Directly connects to bridge acceleration sensor

- Low noise differential amplifier input stage

- Built-in 9 bit temperature sensor A/D

- 4th order digital polynomial computation for offset and gain compensation

- Temperature compensated offset DAC

trimmed to a higher precision, thus avoiding expensive laser trimming. The EEPROM data storage also allows a system re-calibration if the sensor is changed.

During calibration the built-in temperature and external sensors are digitised and transmitted via the UART to the calibration system. This then calculates the required linearisation and offset parameters which are transmitted back to the cell. After testing this data it is written into EEPROM.

- Gain error cancellation DAC

- EEPROM storage for compensation and error cancellation data

- UART Interface for system calibration

- $-40^{\circ}$ C to  $+120^{\circ}$ C operation

- +5V single supply

- Requires no expensive laser trimming

Company

TEMIC

**Dialog Semiconductor**

# ASIC Cells - ACSC

### **Bridge Sensor Conditioning System**

### Description

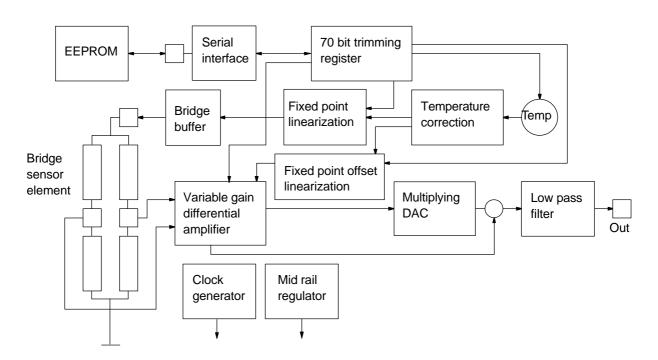

This major ACSC is designed to directly connect to a monolithic bridge sensor and provide a temperature and sensor compensated analog output signal.

A 70 bit shift register is used to store calibration data of all programmable functions. After connecting the cell to a sensor the assembly can be calibrated. This is done by reading the uncalibrated values calculating the required compensation and then writing this data into the shift register. When correct calibration has been achieved the data is written to EEPROM which is then used for normal operation.

The advantage of this concept is that a sensor with wide manufacturing tolerances can be used and electronically trimmed to a high degree of precision. The EEPROM data storage also means that a system can be re-calibrated should the sensor be changed.

### Features

- Works with low-cost bridge sensors

- Built-in temperature sensor, and programmable temperature compensation

- Programmable fixed point sensor linearisation of both bridge drive and offset

- Programmable amplifier gain

- Programmed data stored in EEPROM

- Serial EEPROM interface

- $-40^{\circ}$ C to  $+120^{\circ}$ C operation

- Single +5V supply

- Avoids expensive laser trimming

TEMIC

**Dialog Semiconductor**

ASIC Cells - ACSC

### **Temperature Sensor Conditioning Circuit**

### Description

This major ACSC generates an output voltage linearly proportional to temperature. It is primarily designed for monolithic temperature measurement applications. When combined with sensors having other physical properties (pressure, optical etc.) it can be used to correct their temperature sensitivity.

Most sensors require thermal corrective processing when used over a wide temperature range. The

temperature proportional voltage generated by this cell can be used to compensate for this undesirable effect and allow a higher accuracy of overall measurement.

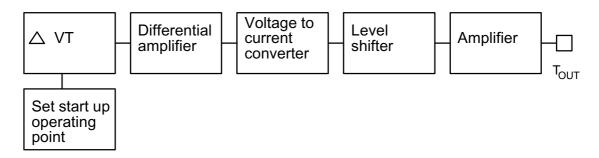

An integrated delta- $V_T$  reference generates a temperature proportional voltage. The voltage is differentially amplified and fed to a series of current mirrors.

### Features

- Linear 19.9mV/<sup>0</sup>C scale factor

- $0.5^{\circ}C$  accuracy at  $+25^{\circ}C$

- Operating temperature range  $-40^{\circ}$ C to  $+95^{\circ}$ C

- Low current consumption means minimal self-heating

- Single +5V supply operation

## **Optical Positioning Sensor**

### Description

This major ACSC is designed primarily to remotely sense mechanical positioning in automotive engine management systems.

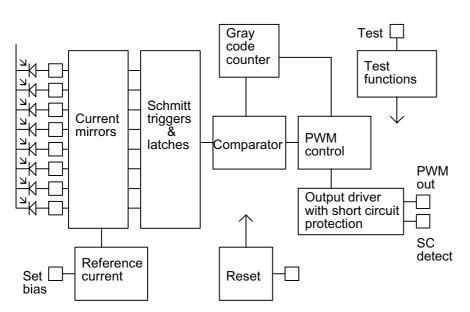

Eight photodiodes connect directly to current sources. Current mirror circuits, together with a common reference current, are externally adjustable. To give reliable operation the optical data is in gray code format. Schmitt trigger inputs are used to improve noise immunity before the data is clocked into a register.

A free-running gray counter turns the Pulse Width Modulator (PWM) on at a fixed counter state. This counter is then compared with the latched optical data. When both are equal the PWM output is switched off, thus producing an output on-time proportional to the read gray code.

By modifying the counter states used together with different counter prescaling factors, it is easy to change both the duty cycle and cycle time of the PWM. The output driver stage incorporates a shunt resistor sensor which shuts the PWM output down upon detection of a short-circuit condition.

An integrated power-on reset ensures that the cell powers-up in a predefined state. It also reduces cable length from the central electronics to the remote sensor. Test mode circuitry enables the cell to be quickly checked for functionality without additional dedicated test outputs.

### Features

- Converts optical gray code into PWM signal

- · On-chip current biasing of sensor photodiodes

- Adjustable photodiode current

- Gray code ensures reliable operation

- Digital PWM allows easy modification of pulse widths

- Short circuit PWM output shuts driver down

- Single wire serial interface reduces system costs; test logic allows fast testing

- On-chip power-on reset

- Single +5V supply

**TEMIC** Dialog Semiconductor

## **PWM Motor Controller**

### Description

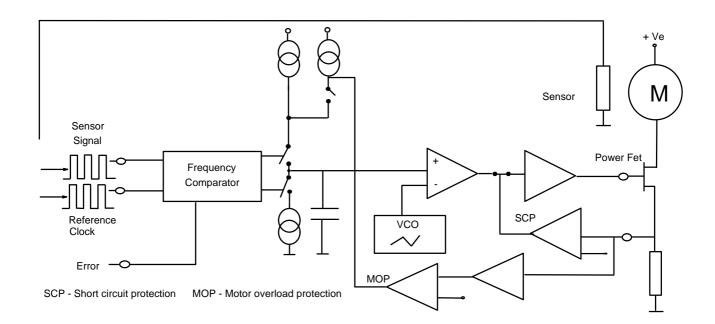

This major ACSC is designed to drive automotive DC universal motors. As a stand alone function it provides accurate speed control based on a variable reference clock input. Motor short circuit conditions are monitored and cause the device to shut-down thus avoiding electrical and mechanical damage. For safety critical applications an alarm output signals motor malfunction. Motor stalling conditions are also monitored and the motor power is proportionally reduced to avoid system damage.

The frequency comparator block compares the actual motor speed with the incoming reference clock. Based upon their relationship a pair of current sources are dynamically switched and integrated with a capacitor. The capacitor charge is thus proportional to the actual motor speed. This variable threshold and a fixed sawtooth oscillator are then fed to a comparator which produces a pulse-width modulated output.

The voltage of an external motor shunt resistance is measured and if too high (motor short condition) shuts the driver stage down. To detect stalling conditions a second comparator is used, which changes the ratio of the current sources such that reduced power is applied to the motor.

Large differences between actual and set motor speeds generate an alarm output which can be used for diagnostic purposes.

#### Features

- Drives low cost universal motors

- Direct on-chip power FET driver

- Closed loop speed control

- Wide speed control range

- Motor short circuit shut-down

- Motor overload protection

- Digital diagnostic alarm output

- Single +5V supply

TEMIC

**Dialog Semiconductor**

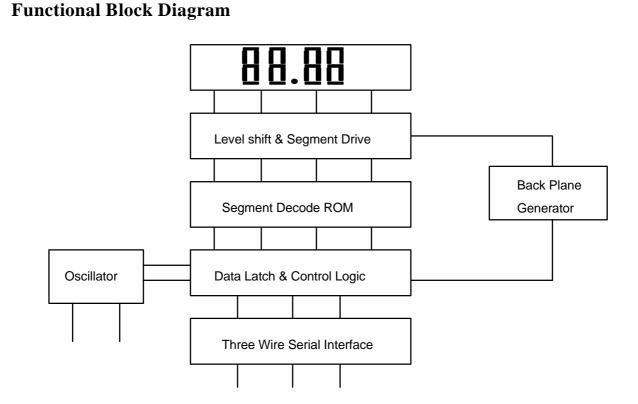

### LCD Display Decoders / Drivers

### Description

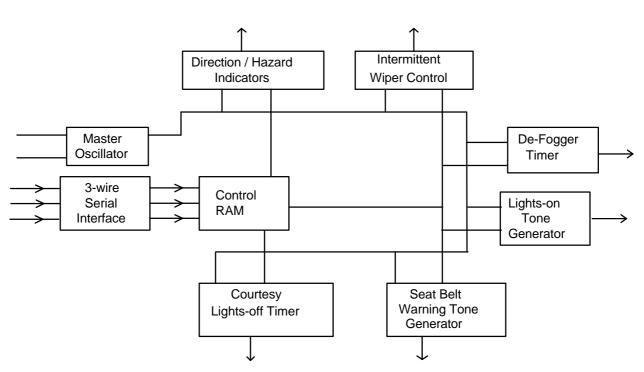

This major ACSC provides all the functions required to take in data either by serial interface or driven directly and decode the data to drive an LCD display. The ACSC can be fully customised to the number of segments per digit and the number of digits per display. All backplane waveforms can be derived from the master oscillator. A power on reset function can also be provided.

### Features

- Drives LCD directly

- 3-wire serial interface

- Backplane waveform generation

- Data latch and ROM decode

- Oscillator and frequency division

- Low power consumption

## Multi-Function Timers

### Description

Multifunction timers that can be customised to suit individual needs are available built from the minor ACSC functions detailed below.

Programming can be by serial interface or by individual pins.

The two pin oscillator is intended for use with crystals and ceramic resonators. As an alternative, the ACSC can be driven from an external clock.

No external filter components required

Single +5V supply

• Low power consumption

### Features

- Multi-function timer suitable for all types of automotive application

- Fully programmable via a three wire serial interface

- Custom configurations available

٠

•

TEMIC

**Dialog Semiconductor**

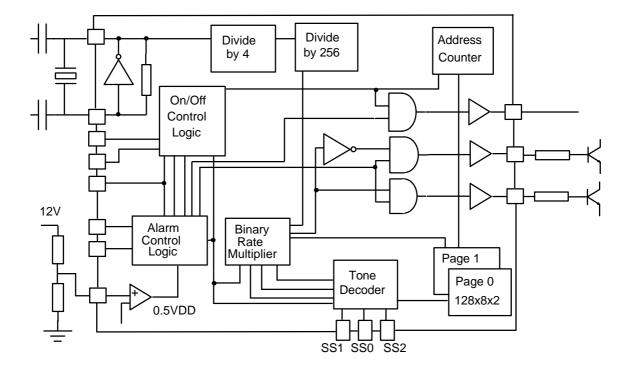

### Siren Tone Generator Cell

### Description

This major ACSC is a stand alone mixed analog/digital circuit which generates a number of pre-defined output waveforms for the purpose of driving the siren in a car-alarm system.

The chip produces a digital output whose frequency is determined by the output of an 8-bit binary-rate multiplier. A total of seven tones are produced. Five of these are fixed tones, and two are determined by the contents of an on-chip ROM. Tone selection is determined by the state of inputs SS0, SS1 and SS2. The selected tone is fed to two output buffers (true and complemented form) which provide the basedrive to two external npn devices which power the horn.

The chip is triggered into alarm mode either by a HIGH on the input pin, or by an internal comparator detecting the voltage on pin VBATT falling below VDD/2. This is intended to detect the removal of the car battery terminal. The alarm control logic pulses the alarm outputs on and off for a period determined by the state of the timer control inputs.

#### Features

- Complete stand alone system

- Generates up to 7 separate alarm sounds

- Meets international standards

- Mask ROM programmable

- Battery removal detection

- Few external components

- Low power

- Small size, compact SO16 package

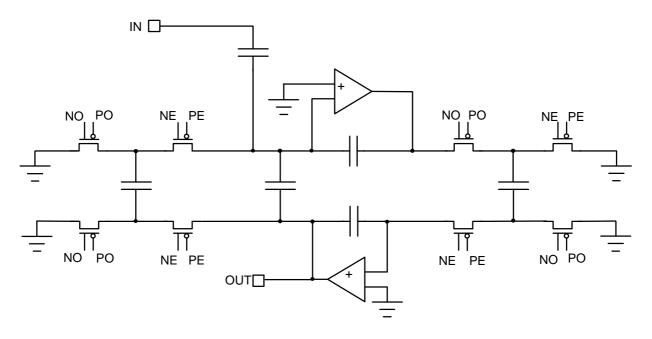

## **Switched Capacitor Filters**

### Description

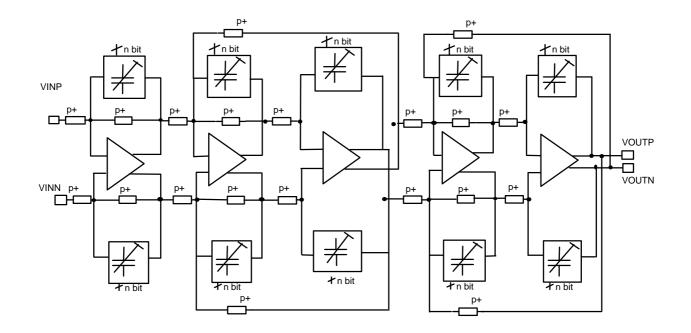

Cascaded biquad or RLC ladder sampled data filters may be provided using switched-capacitor structures with orders from 1 to > 20. For flexible, programmable and area-efficient filter structures, any number of 1st, 2nd and 3rd-order biquad sections may be cascaded and then simulated for effects of supply voltage, process and temperature variations prior to synthesis.

Dynamic range and frequency response can be extended by use of fully differential structures. Sin(x)/x, warping

Features

- Handles signal frequencies from <0.1Hz to >250kHz

- Uses on-chip anti-aliasing filters

- No external (off-chip) components required

- Either  $\pm 5V$ ,  $\pm 5V$  or  $\pm 3V$  supplies may be catered for

and aliasing effects are reduced by pre-warping the filter response and by use of 2nd or 3rd order continuous-time (active RC) filters which are included on chip. Filter sensitivity is reduced by use of ladder, rather than cascaded biquad, SCF structures.

Non-overlapping clock phases required by the SC switches are generated using standard cell circuits.

- Clock phases generated on-chip from just one external (stable) clock

- Gains and pole positions accurate to within 0.05%

- Filters, integrators, differentiators, rectifiers and companders may be realised

### Functional Block Diagram (2nd Order Biquad)

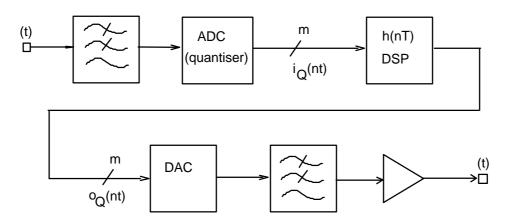

### Description

When reproducible, accurate and/or programmable filtering is required in a single-chip solution a digital filter should be considered. DSP solutions can be provided to a wide range of requirements. These may be used in conjunction with other mixed signal cells such as amplifiers, Continuous Time (CT) filters, ADCs and DACs as exemplified in the schematic below. Using Dialog's DSP Design and Synthesis tools, the filter is designed, optimised and simulated at gate/block level for a bit-true realisation. Finite word-length analysis, limit-cycle investigations and noise analyses are carried out prior to transfer for ASIC routing tools for area-efficient synthesis. VHDL may also be used for design entry, simulation or logic synthesis.

Code is generated for use in prototyping (FPGA or DSP board) when hardware is required prior to silicon availability.

### Features

- Filters of virtually any order may be realised

- Supply voltages of 2.7-5.5V catered for

- Supported by prototyping

- Operation may be programmable

#### • FIR or IIR

- Adaptive filters

- May be used in conjunction with on-chip data-converters for analog-in / analog-out integration

## CT Filters (Trimmable)

### Description

Continuous-time (CT) Filters may be realised in an integrated circuit and this provides a useful function block for anti-aliasing, smoothing, reconstruction, etc. This produces a small-area silicon solution (see datasheet for CT Filters (Anti-alias)) but when accurate filter characteristics or higher order filters are required, an alternative technique (such as mosfet-C or trimmable-pole) must be employed.

The circuit below shows a fifth-order Butterworth lowpass filter using on-chip (polyfuse) trimming of the pole frequencies to ensure better than 10% accuracy in positioning. To maximise the dynamic range, reduce the effect of switching spikes elsewhere in the IC system, and reduce common mode interference, a fully differential structure is shown.

For any chosen filter structure the pole Q is determined by a single resistor ratio so that once all the pole frequencies have been adjusted by a common increment, the pole Q's of individual filter stages can be adjusted to control group delay.

Filters realised in this way may be trimmed during wafer sort and after packaging.

#### Features

- Low noise

- 10% accuracy cut-off (trimmed by polyfuse)

- Frequencies from 1kHz to 5Mhz

- Can be powered down

- High dynamic range (up to 100dB)

- Area efficient

- No external components required

- No clock or PLL required

## **CT Filters (Anti-Alias)**

### **Description**

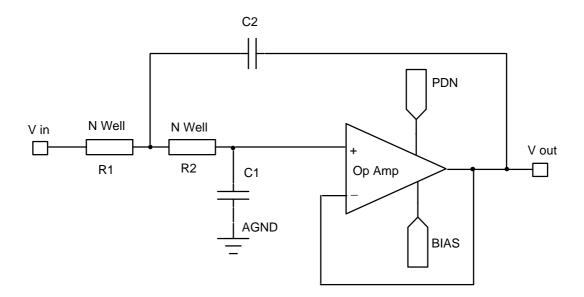

Continuous Time (CT) filters are realised on CMOS integrated circuits by using various resistor structures (e.g. n-well or p-well) in combination with suitable capacitors (e.g. poly1/poly2) and opamps. This form of CT Filter will exhibit pole position uncertainty because of process spreads and values but this variability of "cut-off frequency" of up to 50% can be tolerated in certain applications and designed-in for anti-alias/reconstruction filters used in conjunction with sampled-data signals.

The usual form of integrated CT Filter is 2nd order (high-pass or low-pass) employing the "Sallen & Key"

topology but higher orders may be realised with due consideration given to distortion, cut-off frequency and Q.

Different resistor and capacitor structures may be chosen (depending on the CMOS process used) for a trade-off on size/absolute accuracy/linearity/frequency. A particular benefit of this type of integrated filter is good noise performance.

For CT Filters requiring accurate pole locations methods such as mosfet-C, trimmable R/C, or external R and/or C are available (see CT Filters (Trimmable) datasheet).

### **Features**

- Low noise

- May be powered down

- Wide range of supply voltages •

- ٠ Compact structures (small silicon area)

- For anti-aliasing or reconstruction filter ٠

- Wide range of cut-off frequencies (1kHz to 5Mhz)

- Accurate if used in conjunction with external components or trimming

- Efficient silicon area

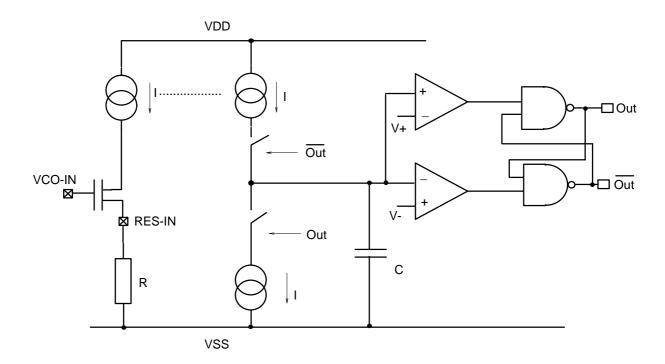

## Linear Voltage Controlled Oscillator (VCO)

### Description

This minor ACSC produces an output signal whose frequency is determined by the voltage at the VCO-IN input, and the resistor connected to the RES-IN input. The resistor and the input voltage define a current within the VCO that is used to charge and discharge an internal capacitor between two threshold voltages.

When used in conjunction with a standard phase/frequency comparator and loop filter components, a phase-locked loop (PLL) can be formed to generate a wide range of frequencies. The use of ratio N/M division can additionally provide a direct frequency synthesis function.

### Features

- Low power (100uA or less)

- Programmable frequency range

- Applications include direct frequency synthesis

- Typical frequencies ~ 1kHz to 5MHz

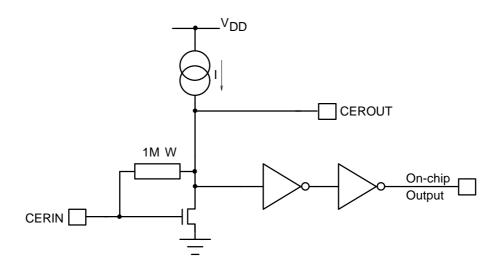

### **Oscillator for Ceramic Resonators**

### Description

This minor ACSC is a 2-pin oscillator based on a single-stage class A amplifier. This minimises the output voltage swing and therefore current/power dissipation.

An internal  $1M\Omega$  (nom.) feedback resistor is provided, saving an external component. The oscillator cell, when used with a resonator with integral load capacitors provides a low-cost and compact stable timebase for many applications.

### Features

- 2 pin oscillator, well suited for use with ceramic resonators

- Frequency range 0.5mhz to 4MHz

- Feedback resistor (1M W) on-chip saves external components

- Operating current 200µA or less at 4MHz

## Crystal Oscillator

### Description

This minor ACSC function is a 2-pin oscillator intended for use with crystals and ceramic resonators.

An internal 1 M $\Omega$  (nom.) feedback resistor saves an external component and simplifies board layout.

The output of the oscillator can be buffered and brought off-chip through a suitably-sized driver to provide a system clock to the rest of the board.

### Features

- 2 pin oscillator, suited to use with ceramic resonators from 6 to 12MHz, or crystals up to 20MHz

- Internal 1 M $\Omega$  (nom.) feedback resistor saves external component

- Operating current with 12MHz resonator typically 1.5mA

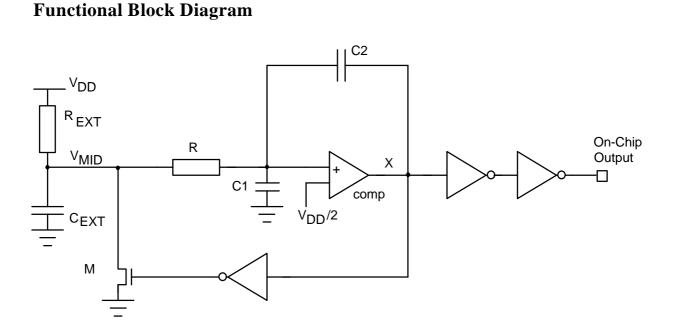

### **Functional Block Diagram**

OSCIN OSCOUT

### **RC** Oscillator

### Description

This minor ACSC function is a 1-pin relaxation oscillator. Frequency variations for f < 1kHz is primarily set by external components.

$t_{\rm osc} = 0.693 \; (R_{\rm EXT} \; C_{\rm EXT} + 6 \mu s)$

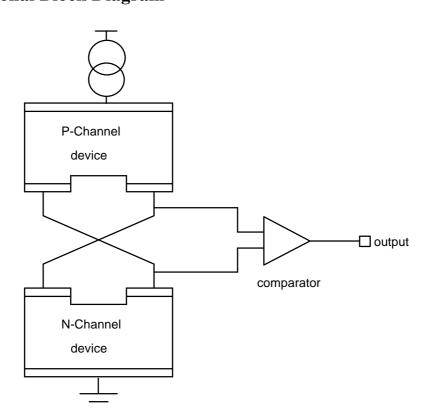

As  $V_{MID}$  crosses VDD/2, comp output x goes high, switching on the pull down device M, for time RC1, completely discharging  $V_{MID}$  to 0V. M then switches off, causing  $V_{MID}$  to charge up towards VDD again.

### Features

- Single-pin oscillator, suitable for generating lowfrequency clocks (<1 kHz)

- Frequency determined by external R and C

- Low operating current (for R = 1MΩ, C = 4.7nF, f = 310Hz, I<sub>DD</sub> = 35µA)

## Low Impedance Driver

### Description

This minor ACSC function is an audio frequency 3 stage buffer with  $\pm$  12mA output current capability designed specifically to drive low impedance loads such as dynamic transducers.

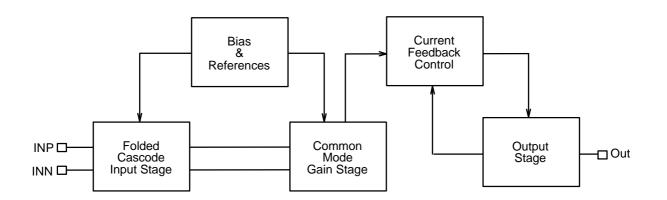

A double folded cascode input stage provides high front end gain for the intermediate common mode gain stage.

Complementary source followers provide gate drive to the output MOSFETs whilst minimising crossover distortion normally associated with class B output stages.

#### Features

- High current drive buffer provides 4Vpp output into 180Ω with <0.5% THD (Vdd ≥ 4.8V)</li>

- Three stage design with current feedback control only takes 300µA typical quiescent current

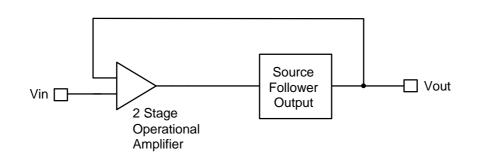

### **Functional Block Diagram**

Supply current is minimised by use of a quiescent current feedback control block which monitors the output device current and adjusts the drive to the source followers whilst maintaining stability.

The buffer is internally compensated and will drive capacitive loads up to 100pF rail to rail.

- 105dB open loop gain 200kHz unity gain bandwidth 90dB PSRR at 1kHz

- Pair of drivers may be used to drive load differentially

### Low Noise Amplifier

### Description

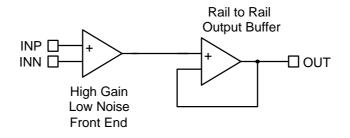

This minor ACSC function is a MOSFET input low noise amplifier with rail to rail output buffer, designed for applications requiring a high input impedance.

The front end consists of P-channel cascoded input devices which have been sized with their loads to provide low flicker noise (1/f knee <100Hz).

Features

- High input impedance, low noise amplifier

- Configured with gain for optimum low noise path

- Cascoded front end provides >80dB PSRR up to 4kHz

### **Functional Block Diagram**

Noise performance is suitable for critical applications; equivalent input referred noise from 50Hz - 3.4kHz is  $1.6\mu$ Vrms. Supply rejection exceeds 80dB across this band.

Thermal noise is <25 nV/Hz<sup>1/2</sup>.

The output buffer provides low distortion (<0.05% THD) for  $\pm$  2.0V in to 10k $\Omega$ /50pF.

- Supply current of 320µA, Vdd(min) of 4.8V

- Open loop gain of 120dB, Unity Gain BW of 1MHz

## **Rail to Rail Amplifier**

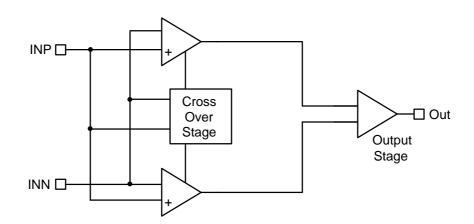

### Description

This minor ACSC function is an internally compensated, unity gain stable buffer.

True rail to rail operation is achieved by twin input stages with a low-gm, low distortion input crossover stage.

The pseudo push-pull output stage provides low distortion with low  $(250\mu A)$  quiescent current.

Open loop gain and bandwidth are 96 dB, 1MHz respectively.

### Features

- Dual input stage gives rail to rail input common mode range

- Rail to rail output for capacitive loads up to 50pF

- $\pm 1.9$ V into  $10k\Omega$  load;  $\pm 0.7$ V into  $2.5k\Omega$  load (Vdd=4.8V, THD $\leq 0.03\%$ )

- Low supply voltage (2.7V) capability with rail to rail operation

- Higher output drive variant available (±2.1V<sub>pk</sub> into 1KΩ, Vdd=4.8V, 500µA quiescent)

### **Mid-Reference Buffer**

### Description

This minor ACSC function is a unity gain analog ground buffer with complementary source follower outputs, providing matched output current capability.

Internally compensated to remain stable for capacitive loads up to 100pF.

Features

- Less than 0.1% load regulation at 2.5V for 2.4mA output current

- Equal output current source and sink capability

### **Functional Block Diagram**

Nominal open loop gain and bandwidth is >75 dB and 600KHz respectively.

- Low quiescent current 250µA

- High input resistance from MOSFET inputs

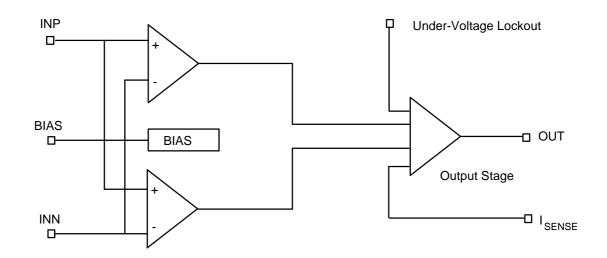

### **Driver Amplifier**

### Description

This minor ACSC is an internally compensated, unity gain stable buffer.

Complementary input stages provide rail to rail input common mode range. A pseudo push pull output stage provides low distortion with low quiescent current. Higher output drive variants are available as defined by the required specification.

#### Features

- Operating Temp Range: -40 to +125 deg C

- Operating Voltage Range: -4.5 to 11V

- Open loop gain and bandwidth are 90db and 250kHz respectively

- Drives <u>+</u>5V into 2k load (V<sub>DD</sub>=11V); Rail to rail output for capacitive loads up to 100pf

- Under voltage lockout and short circuit protection circuitry compatible

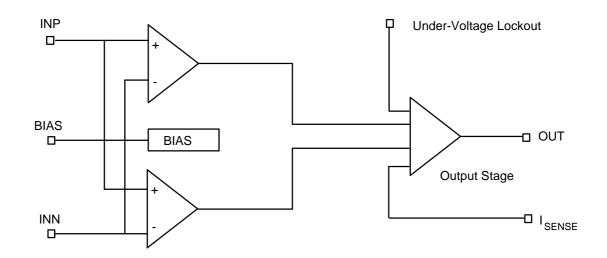

### **Driver Amplifier**

### Description

This minor ACSC is an internally compensated, unity gain stable buffer.

Complementary input stages provide rail to rail input common mode range. A pseudo push pull output stage provides low distortion with low quiescent current. Higher output drive variants are available as defined by the required specification.

#### Features

- Operating Temp Range: -40 to +125 deg C

- Operating Voltage Range: -4.5 to 11V

- Open loop gain and bandwidth are 90db and 250kHz respectively

- Drives <u>+</u>5V into 2k load (V<sub>DD</sub>=11V); Rail to rail output for capacitive loads up to 100pf

- Under voltage lockout and short circuit protection circuitry compatible

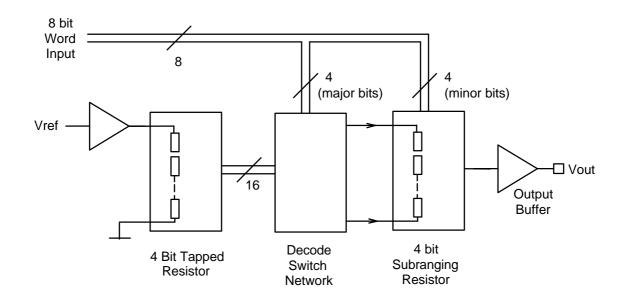

## **General Purpose DAC**

### Description

This minor ACSC function is a medium speed CMOS 8 bit resistor sub ranging DAC with buffered voltage output.

Depending on the input code a 16 element sub ranging resistor (SubR) is connected across two adjacent taps of a 16 element tapped resistor. The four major bits determine the position of the SubR resistor on the

tapped resistor whilst the minor bits decode the sub ranging resistor itself.

The tapped resistor is connected between an internal reference and ground in order to ease the input common mode range requirements of the output buffer.

The choice of the output buffer is dependant on the load and speed requirements: e.g.  $2\mu s$  settling into 200pF with 5V output range.

### Features

- CORE settling time typically 1µs

- $\pm 1/2$  lsb differential non-linearity

- Full scale output adjustable by varying gain of buffer

- Core quiescent current nominally 400µA

## **General Purpose ADC**

### Description

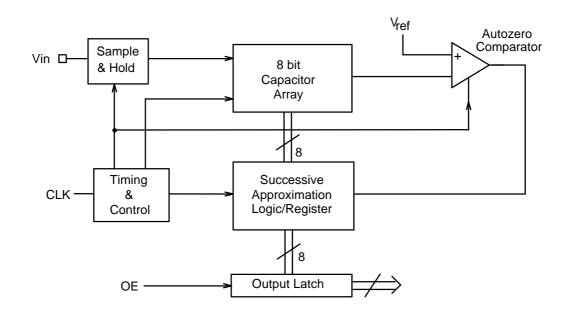

This minor ACSC function is a CMOS 8-bit linear successive-approximation charge-redistributed ADC with auto-zero and internal sample and hold.

During the first half of the conversion period, the input signal is buffered and sampled onto a hold capacitor whilst the comparator is auto zeroed.

The conversion itself proceeds on a successive approximation basis by sequentially switching

Features

- Typically 3µs conversion time

- $\pm 1/2$  lsb differential non-linearity

**Functional Block Diagram**

- 0V to  $V_{DD}$  analog input range with sample and hold

- Inputs may be multiplexed

The required 8 bit binary result appears at the output of the SAR block at the end of conversion and may be latched.

progressively smaller capacitors until the output of the

controlled by

approximation logic which makes a decision for each

the

The

successive

capacitor array equals the reference V<sub>ref</sub>.

switching

is

bit based on the comparator output.

- Slew rate, tracking is typically 2.5V/µs

- Quiescent supply current nominally 500µA

## High Resolution ADC

### Description

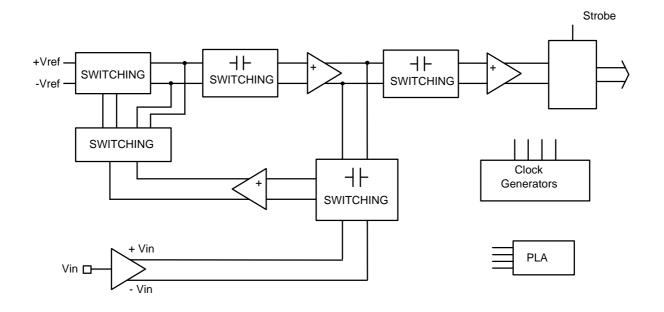

A basic cyclic converter can achieve a limited resolution due to the inaccuracy of the times 2 multiplier, the sample/hold feedthrough, and the amplifier gain used in its construction. This minor ACSC function is a high-resolution converter which removes these inaccuracies while still using the sequential conversion technique of any cyclic converter. Thus the rate of conversion is determined by the required resolution and the settling time but, now, conversion can be made to exceed 12 bits with 1 LSB integral non-linearity.

The reference voltage (initially set equal to the MSB) is rotated around the converter loop, interleaved with the

normal cyclic conversion algorithm. This causes the reference voltage to be subjected to the same converter loop tolerances (identified above) as the processed signal. This also relaxes the tolerance and size of the capacitors. Each bit of conversion must take 8 clock cycles in this converter and so the 12 bits requires 96 clock cycles in total. The structure used on this chip employs differential circuitry throughout and the capacitors are switched around the opamps to provide the functions of comparison, subtraction and multiply by 2. The switching and sequencing is provided by an on-chip PLA.

#### Features

- 12 bits resolution

- Single-chip solution with no external components except crystal oscillator

- Conversion rate of greater than 10kHz

- $\pm 5V$  supply

- No 'calibrate cycle' required

- Built in sample/hold

- Low power consumption (15mW)

### Description

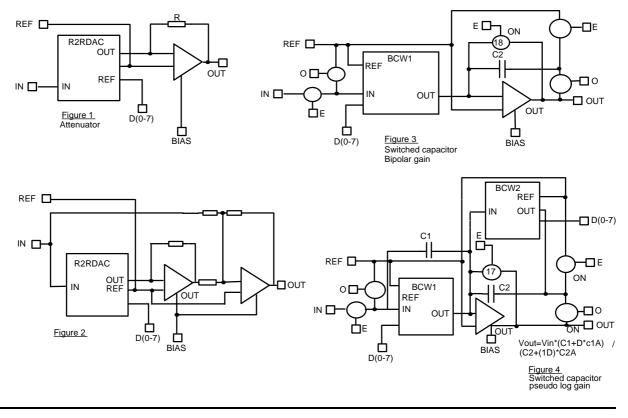

Multiplying DACs are used to provide digitally controlled gain or attenuation.

The basic configuration shown in Fig. 1 uses an R-2R DAC in current steering mode and a trans-resistance stage with feedback resistor equal to R to provide a digitally controlled attenuator with a bandwidth determined by the amplifier. The addition of an amplifier, as in Fig. 2 gives bipolar operation.

For switched capacitor circuits, the R-2R DAC is replaced by a binary weighted capacitor array as shown in Fig. 3. The circuit provides bi-polar gain /

attenuation, where the inversion is achieved by changing the input switch phases.

In applications requiring logarithmic gain/attenuation increments the circuit of Fig. 4 can be used to provide an approximately logarithmic variation between gains A1 and A2 if:

$$\frac{C1}{C2} = \sqrt{A1 \times A2}, \frac{C1A}{C2} = A1 - \sqrt{A1 \times A2}$$

$$\frac{C2A}{C2} = \sqrt{\frac{A2}{A1}} - 1$$

#### Features

- Digitally controlled gain or attenuation

- Unipolar and bipolar configurations

- Continuous time and switched capacitor circuits

- Approximately logarithmic gain step circuit

# ASIC Cells - ACSC

## **Band-Gap Reference**

### Description

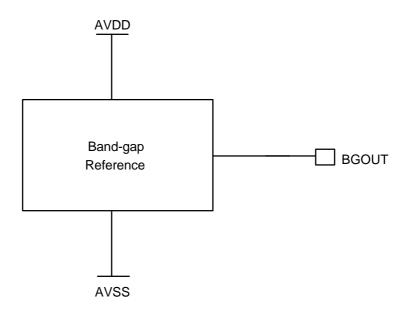

This minor ACSC function is a CMOS Band-gap reference cell for use as an on-chip voltage reference.

The cell uses vertical pnp transistors in the band-gap cell to reduce output voltage spread. A low offset and low noise bipolar amplifier is used to provide the loop gain. The cell has an output impedance of 5k ohm so the output should be buffered for load currents exceeding  $10\mu A$ .

### Features

- 1.24 Volt reference  $\pm 4\%$

- Supply voltage range 2.5V to 6V

- Temperature coefficient  $< 100 \text{ ppm/}^{\circ}\text{C}$

#### • Power supply rejection ratio of >60dB

• Undecoupled output noise  $< 500\mu$ V r.m.s.

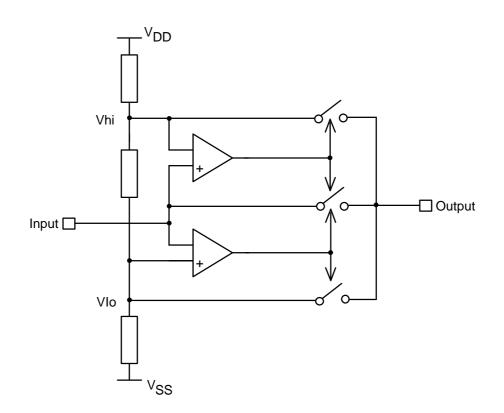

### Description

This minor ACSC function is a limiter consisting of two comparators and three switches that clamp the output to the high and low limiting voltages. This type of circuit operates with signals from DC to audio frequencies. The speed of the comparator will determine the upper frequency response of the limiter.

The reference voltages can either be generated as a ratio of the supply voltages, as shown, or derived from a known reference, for example a bandgap.

### Features

• Operates from DC to audio frequencies

• Limiting levels set by resistor ratio

### Description

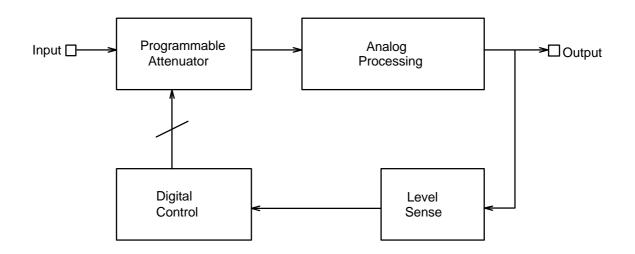

This minor ACSC function is a soft limiter consisting of a gain stage, level sense and digital controller in a closed loop. The signal amplitude is controlled using a digitally programmable attenuation stage driven from an up/down counter. The attack and decay rates are set in the up/down count speed. The level sensing occurs after any system signal processing (for example filtering) and causes the digital control to count up when the preset limit is exceeded.

### Features

- Attack / decay time set in digital controller

- Level sensing requires only a simple comparator

### **Functional Block Diagram**

• Preset limit for the sense can easily be made ratiometric with supply voltage

**Full Wave Rectifier**

### Description

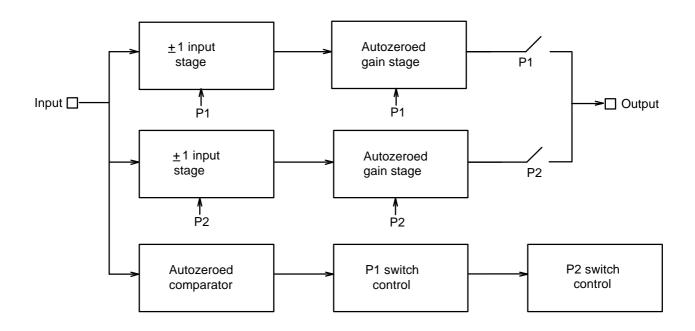

This minor ACSC function is a full wave rectifier, built using two interleaved rectifiers to generate a continuous output. Each rectifier consists of a  $\pm 1$  gain stage followed by an autozeroed switched capacitor gain stage. This cancels any amplifier input offset, and gives an accurate gain (due to the matching of the capacitor ratio). The polarity of the input is sensed using an autozeroed comparator that drives the P1 and P2 switch control circuits.

### Features

- Low input offset circuit

- Continuous output

• Accurate gain due to SC structure

## **Battery Voltage Detector**

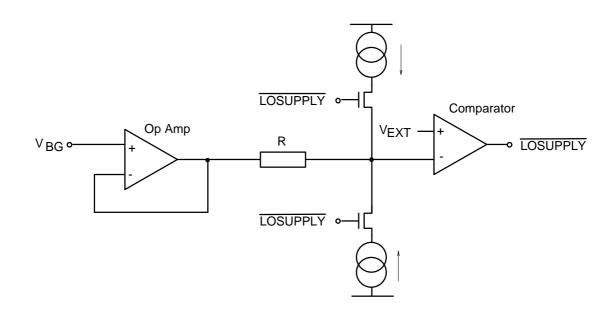

### Description

This minor ACSC function is a battery voltage monitor where a buffered bandgap reference voltage is compared to an external voltage, and output LOSUPPLY goes low when  $V_{EXT} < V_{TRIP}$ . The use of the bandgap reference voltage allows an accurate and temperature stable threshold to be defined.

The positive trip level, as  $V_{EXT}$  falls towards  $V_{BG}$ , is  $V_{BG}$ - IR. When  $V_{EXT} < V_{BG}$ - IR, LOSUPPLY goes low, moving  $V_{TRIP}$  to  $V_{BG}$ + IR. Appropriate choice of I and R allows any noise on  $V_{EXT}$  to be rejected, and not cause false triggering of LOSUPPLY.

### Features

- Comparator and bandgap reference voltage allows accurate voltage detection

- Incorporates hysteresis to prevent false triggering and output glitches

- Use of external potentiometer allows voltages outside of the supply range of the device to be monitored

- Useful in low battery voltage detection circuits

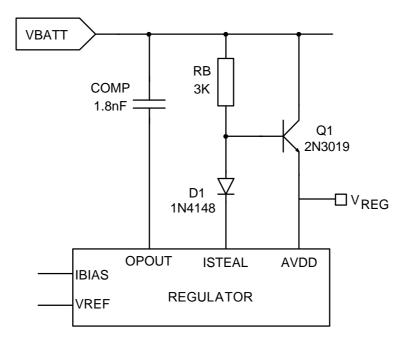

## Voltage Regulator

### Description

This minor ACSC function is a 5V voltage regulator and requires just 1 resistor, 1 diode, 1 npn transistor and 1 capacitor to function. It is capable of providing up to 12mA at 5V. The output is accurate to 10% over the temperature range 0-70°C and for input voltages between 6V and 16V.

### Features

- 6-16V input voltage range

- $5V \pm 10\%$  output voltage

- 12mA current capabilityUses just 4 external components

- e ses just i external compo

ASIC Cells - ACSC

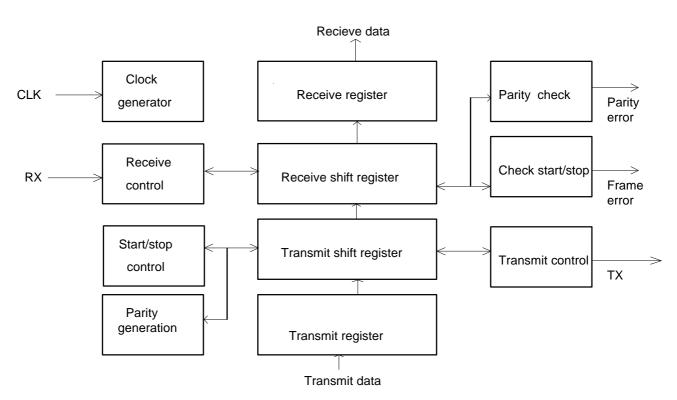

### **Diagnostic Universal Asynchronous Receiver Transmitter**

### Description

This major ACSC allows, with a minimum external connections, the transfer of large amounts of data to and from mixed signal ASICS.

The UART function is an industry standard serial interface and is implemented in many micro-controller

devices. It allows 8 bit data to be asynchronously transferred bi-directionally between 2 systems. The data is transparently processed by the UART which means there is no protocol overhead in such a system.

#### Features

- Compatible with industry standard UARTs

- Duplex operation

- Start, stop and parity generation and recognition

- Cost effective solution for connecting mixed signal ASICs to computer diagnostic aids

- $-40^{\circ}$ C to  $+120^{\circ}$ C operation

- Single +5V supply

### Hall Effect Switch

### Description

The Hall Effect switch is based on two MOS devices with split drains. With a magnetic field perpendicular to the silicon, the path of the majority carriers in the MOS channels are deflected. When the two devices drains cross coupled, the paths for the positive charged 'holes' and negative charged 'electrons' are deflected in opposite directions which causes a differential output. A comparator then detects the differential output to give a north or south pole indication.

Applications for this device include position sensing, revolution counters, etc.

Due to the small size the circuit is easily embedded within additional circuitry to give an intelligent sensor.

• Temperature and process compensated design

#### Features

- Small area

- North/South pole output

- Functional Block Diagram